# MS11-P MOS Memory

**Technical Manual**

Prepared by Educational Services of Digital Equipment Corporation Copyright 0 1982 by Digital Equipment Corporation

# All Rights Reserved

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts Ø1754.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| DEC          | DECnet       | OMNIBUS |

|--------------|--------------|---------|

| DECUS        | DECsystem-10 | OS/8    |

| DIGITAL      | DECSYSTEM-20 | PDT     |

| Digital Logo | DECwriter    | RSTS    |

| PDP          | DIBOL        | RSX     |

| UNIBUS       | EduSystem    | VMS     |

| VAX          | IAS          |         |

0

ς,

6

| CHAPTER 1                                                                                                                                                                              | CHARACTERISTICS AND SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.3<br>1.3.1<br>1.3.1<br>1.3.2<br>1.3.3<br>1.4                                                                                                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                        |

| CHAPTER 2                                                                                                                                                                              | INSTALLATION AND PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.1<br>2.2<br>2.2.1<br>2.2.1.1<br>2.2.1.2<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.4<br>2.2.4.1<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.6<br>2.3.6.1<br>2.3.6.2<br>2.3.6.3 | General2-1Installation2-1Switch and Jumper Configuration2-1Memory Addressing2-3CSR Address Selection2-6Backplane Placement2-8Power Voltage Check2-8MAINDEC Testing2-11Test Procedure2-11CSR Bit Assignment2-13Uncorrectable Error Indication Enable2-13Disable Correction Mode2-13Diagnostic Check Mode2-15Single Error2-15Error Address and Check Bit Storage2-15UNIBUS Address Storage2-16EUB Address Storage2-16 |

| 2.3.6.4<br>2.3.7<br>2.3.8<br>2.3.9<br>2.3.10<br>2.3.11<br>2.3.12                                                                                                                       | Syndrome Storage                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                        | Summary Data Condition Tables                                                                                                                                                                                                                                                                                                                                                                                       |

2

ø

3

# CHAPTER 3 TECHNICAL DESCRIPTION

| 3.0              | Introduction                                           |

|------------------|--------------------------------------------------------|

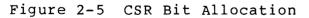

| 3.1              | Block Diagram Description 3-1                          |

| 3.1.1            | UNIBUS                                                 |

| 3.1.2            | Data Bus 3-3                                           |

| 3.1.2.1          | Data Bus Transceivers                                  |

| 3.1.2.2          | Data Latches                                           |

| 3.1.2.3          | EDC Logic 3-3                                          |

| 3.1.2.4          | CSR Logic 3-3                                          |

| 3.1.3            | Memory Address Selection 3-4                           |

| 3.1.3.1          | Address Bus Receivers                                  |

| 3.1.3.2          | Address Latches 3-4                                    |

| 3.1.3.3          | Memory and CSR Select Decoder                          |

| 3.1.3.4          | CSR Address Decoder 3-5                                |

| 3.1.3.5          | RAS Bank Selection                                     |

| 3.1.3.6          | RAS Drivers                                            |

| 3.1.3.7          | CAS Write Enable Drivers                               |

| 3.1.3.8          | Array Addressing Muxes Array Addressing Muxes          |

| 3.1.3.9          | Array Address Drivers                                  |

| 3.1.3.10         | Memory Array 3-5                                       |

| 3.1.4            | Memory Control Circuits                                |

| 3.1.4.1          | UNIBUS Control Logic                                   |

| 3.1.4.2          | Microsequencer Timer Microsequencer 3-6                |

| 3.1.4.3          | DIAG (Diagnostic) Decoder                              |

| 3.1.4.4          | Microsequencer 3-6                                     |

| 3.1.4.5          | Battery Backup Switch                                  |

| 3.1.4.6          | Refresh Oscillator                                     |

| 3.1.4.7          | Refresh Arbitration Logic                              |

| 3.1.4.8          | Refresh Counter                                        |

| 3.2              | Detailed Descriptions 3-7                              |

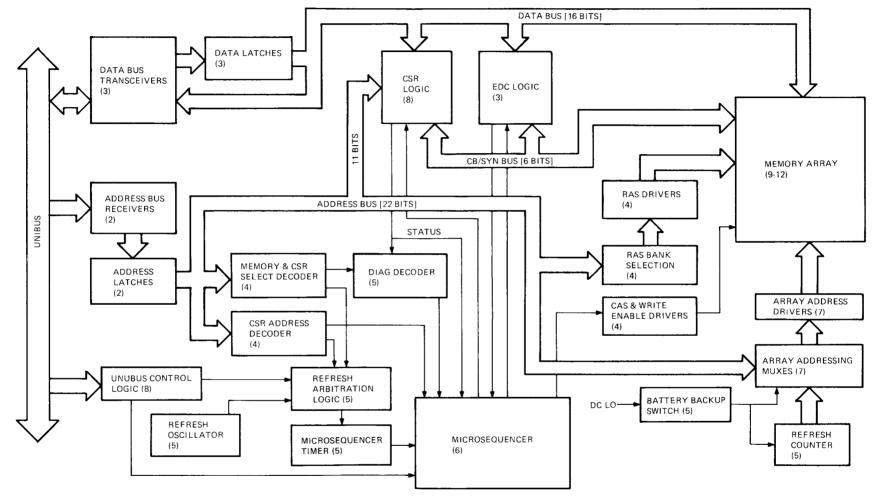

| 3.2.1            | Memory ICs and Memory Array 3-7                        |

| 3.2.1.1          | Dynamic Memory with Multiplexed                        |

|                  | Addressing 3-7                                         |

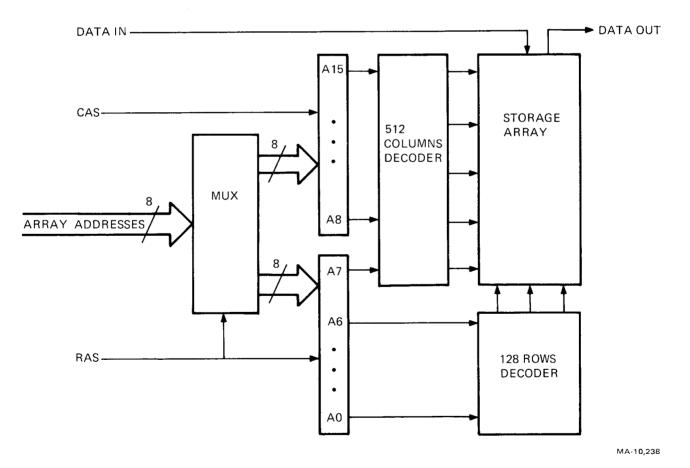

| 3.2.1.2          | Check Bits and Error Correction 3-9                    |

| 3.2.2            | Error Detection and Correction Logic 3-9               |

| 3.2.3            | Control and Status Register Logic 3-13                 |

| 3.2.4<br>3.2.4.1 | Memory and CSR Select Decoder                          |

| 3.2.4.2          | Memory Address Selection                               |

| 3.2.4.2          | Memory Address Decoder                                 |

| 3.2.5            | Other Outputs from the Decoder                         |

| 3.2.6            | UNIBUS Control Logic 3-21<br>Microsequencer Timer 3-23 |

| 3.2.6.1          |                                                        |

| 3.2.7            | Busy                                                   |

| 3.2.8            | Diagnostic Decoder 3-25                                |

| 3.2.9            | Microsequencer                                         |

| 3.2.1Ø           | Battery Backup Switch                                  |

| 3.2.10.1         | Microsequencer Timer Hold-off Circuit                  |

| J• Z • IV • I    | in Refresh Arbitration Logic                           |

|                  | In Refresh Arbitration Logic                           |

G

.

C

# CHAPTER 4 MAINTENANCE

| 4.1<br>4.2<br>4.2.1<br>4.2.2 | General                     |

|------------------------------|-----------------------------|

| 4.2.3                        | MAINDEC Testing 4-2         |

| 4.3                          | Corrective Maintenance 4-2  |

| 4.3.1                        | Initial Check 4-2           |

| 4.3.2                        | Refresh Cycle Check 4-3     |

| 4.3.3                        | Read/Write Check 4-4        |

| 4.3.4                        | Data Shorts Check 4-4       |

| 4.3.5                        | Address Circuits Check 4-4  |

| 4.3.6                        | Toggle in Memory Test       |

| 4.3.7                        | Diagnostic Check Mode Usage |

| 4.3.8                        | Clearing a Double Error 4-6 |

APPENDIX A GLOSSARY AND NOTES

# APPENDIX B HANDLING ELECTROSTATIC SENSITIVE DEVICES

#### FIGURES

4

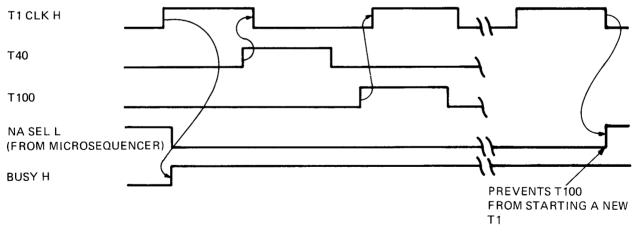

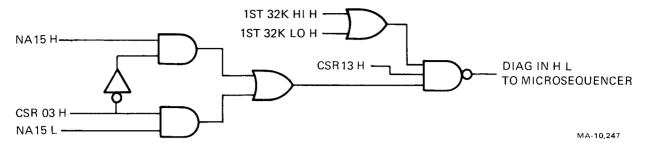

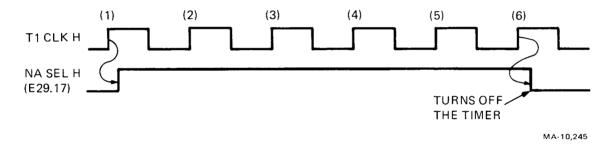

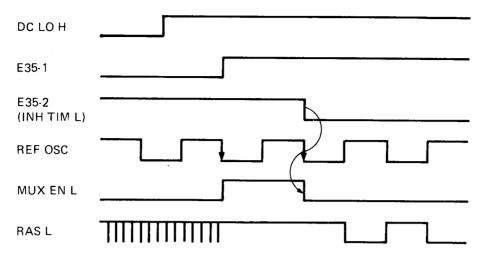

| 2-3Bus Accessible Data Locations2-42-4Octal and Binary Address2-52-5CSR Bit Allocation2-143-1MS11-P Block Diagram3-23-2DRAM Addressing Concept Block Diagram3-83-3EDC Logic Block Diagram3-103-4CSR Block Diagram3-143-5Address Space on 128K Boundary3-183-6Address Space on 8K Boundary3-193-7Microsequencer Timer Simplified Schematic3-243-8Microsequencer Timer Timing Diagram3-263-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32 | 2-1  | Switch and Jumper Locations 2-2                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------|

| 2-4Octal and Binary Address2-52-5CSR Bit Allocation2-143-1MS11-P Block Diagram3-23-2DRAM Addressing Concept Block Diagram3-83-3EDC Logic Block Diagram3-103-4CSR Block Diagram3-143-5Address Space on 128K Boundary3-183-6Address Space on 8K Boundary3-193-7Microsequencer Timer Simplified Schematic3-243-8Microsequencer Timer Timing Diagram3-263-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                    | 2-2  | PDP-11 Data Word 2-3                           |

| 2-5CSR Bit Allocation2-143-1MS11-P Block Diagram3-23-2DRAM Addressing Concept Block Diagram3-83-3EDC Logic Block Diagram3-103-4CSR Block Diagram3-143-5Address Space on 128K Boundary3-183-6Address Space on 8K Boundary3-193-7Microsequencer Timer Simplified Schematic3-243-8Microsequencer Timer Timing Diagram3-263-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                  | 2-3  | Bus Accessible Data Locations 2-4              |

| 2-5CSR Bit Allocation2-143-1MS11-P Block Diagram3-23-2DRAM Addressing Concept Block Diagram3-83-3EDC Logic Block Diagram3-103-4CSR Block Diagram3-143-5Address Space on 128K Boundary3-183-6Address Space on 8K Boundary3-193-7Microsequencer Timer Simplified Schematic3-243-8Microsequencer Timer Timing Diagram3-263-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                  | 2-4  | Octal and Binary Address 2-5                   |

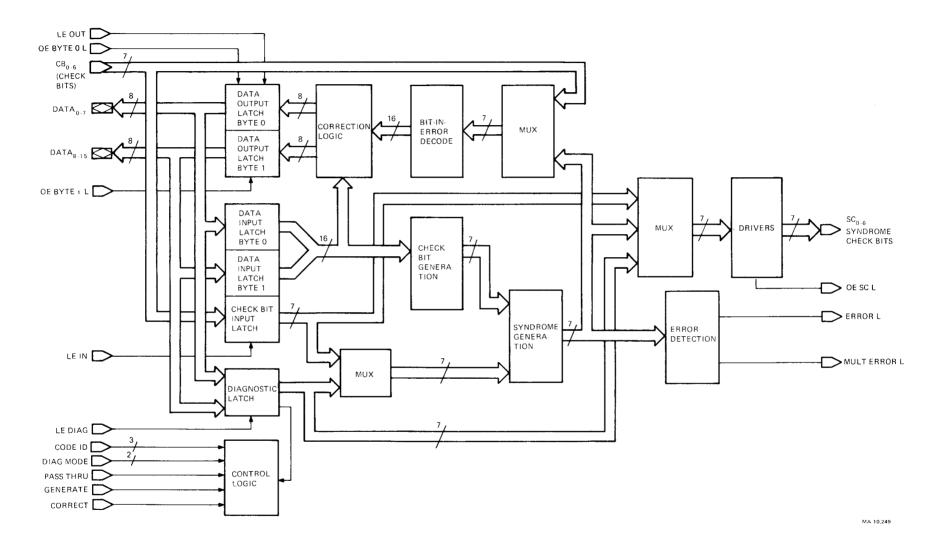

| 3-2DRAM Addressing Concept Block Diagram3-83-3EDC Logic Block Diagram3-103-4CSR Block Diagram3-143-5Address Space on 128K Boundary3-183-6Address Space on 8K Boundary3-193-7Microsequencer Timer Simplified Schematic3-243-8Microsequencer Timer Timing Diagram3-243-9Diagnostic Decoder (Redrawn)3-263-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                                  | 2-5  | CSR Bit Allocation 2-14                        |

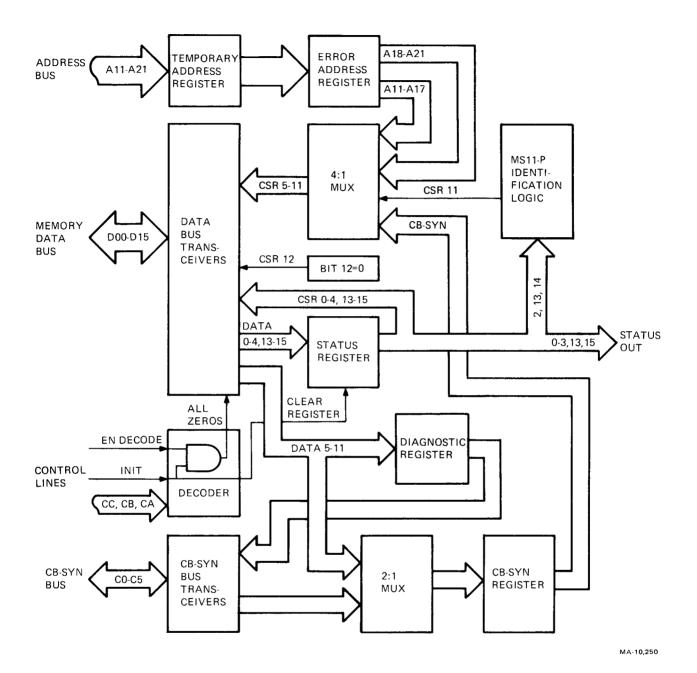

| 3-3EDC Logic Block Diagram3-103-4CSR Block Diagram3-143-5Address Space on 128K Boundary3-183-6Address Space on 8K Boundary3-193-7Microsequencer Timer Simplified Schematic3-243-8Microsequencer Timer Timing Diagram3-243-9Diagnostic Decoder (Redrawn)3-263-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                                                                             | 3-1  | MS11-P Block Diagram 3-2                       |

| 3-4CSR Block Diagram3-143-5Address Space on 128K Boundary3-183-6Address Space on 8K Boundary3-193-7Microsequencer Timer Simplified Schematic3-243-8Microsequencer Timer Timing Diagram3-243-9Diagnostic Decoder (Redrawn)3-263-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                                                                                                           | 3-2  | DRAM Addressing Concept Block Diagram 3-8      |

| 3-5Address Space on 128K Boundary3-183-6Address Space on 8K Boundary3-193-7Microsequencer Timer Simplified Schematic3-243-8Microsequencer Timer Timing Diagram3-243-9Diagnostic Decoder (Redrawn)3-263-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                                                                                                                                   | 3-3  | EDC Logic Block Diagram 3-10                   |

| 3-6Address Space on 8K Boundary3-193-7Microsequencer Timer Simplified Schematic3-243-8Microsequencer Timer Timing Diagram3-243-9Diagnostic Decoder (Redrawn)3-263-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                                                                                                                                                                        | 3-4  | CSR Block Diagram 3-14                         |

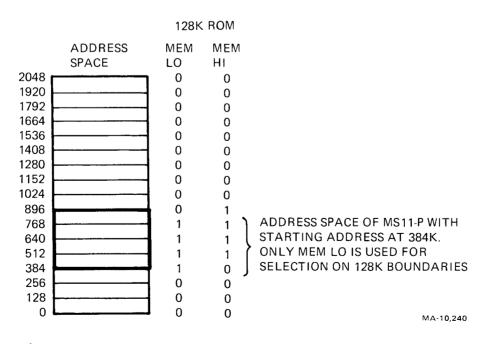

| 3-7Microsequencer Timer Simplified Schematic3-243-8Microsequencer Timer Timing Diagram3-243-9Diagnostic Decoder (Redrawn)3-263-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                                                                                                                                                                                                           | 3-5  | Address Space on 128K Boundary 3-18            |

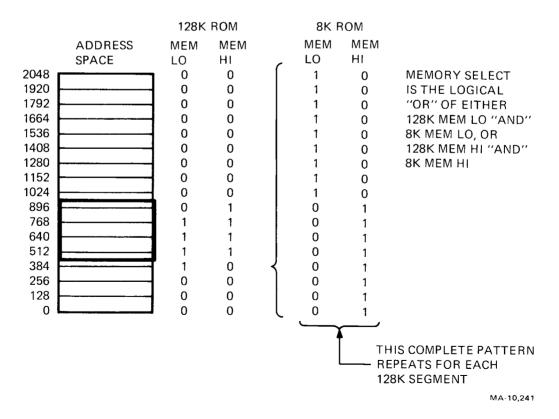

| 3-8Microsequencer Timer Timing Diagram3-243-9Diagnostic Decoder (Redrawn)3-263-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                                                                                                                                                                                                                                                           | 3-6  | Address Space on 8K Boundary 3-19              |

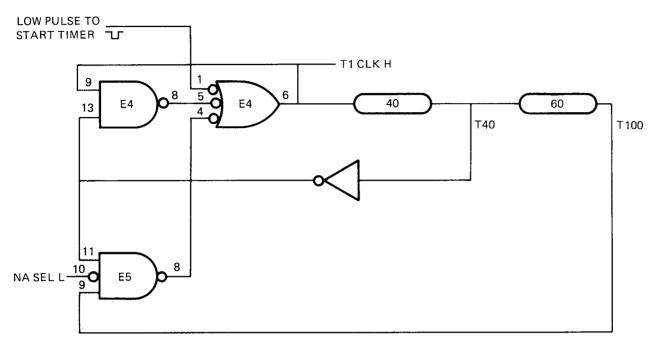

| 3-9Diagnostic Decoder (Redrawn)3-263-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                                                                                                                                                                                                                                                                                                     | 3-7  | Microsequencer Timer Simplified Schematic 3-24 |

| 3-10DATI and Microsequencer Timer3-273-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                                                                                                                                                                                                                                                                                                                                        | 3-8  | Microsequencer Timer Timing Diagram 3-24       |

| 3-11Start of Battery Backup Mode3-313-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-9  | Diagnostic Decoder (Redrawn) 3-26              |

| 3-12End of Battery Backup Mode3-323-13E9 Simplified Schematic3-32                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-10 | DATI and Microsequencer Timer 3-27             |

| 3-13 E9 Simplified Schematic 3-32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-11 | Start of Battery Backup Mode 3-31              |

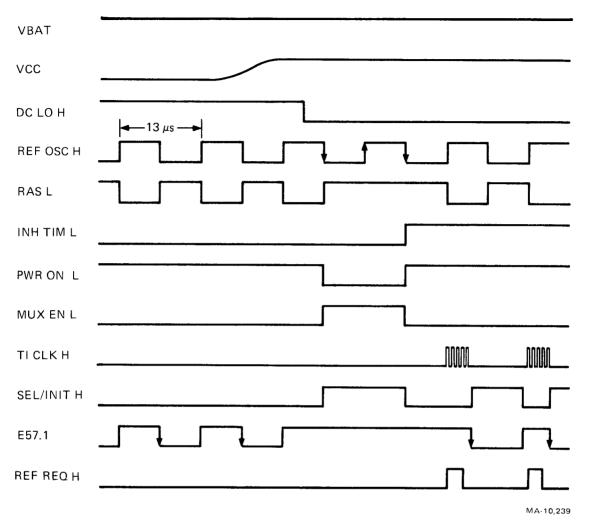

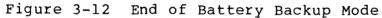

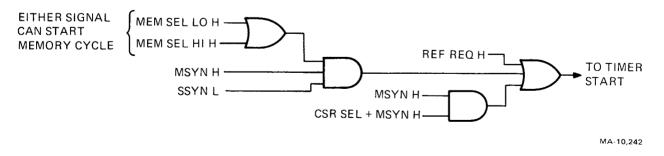

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-12 | End of Battery Backup Mode 3-32                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-13 | E9 Simplified Schematic 3-32                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-1  | Refresh Cycle Check 4-3                        |

# TABLES

| 1-1  | Access and Cycle Times1-5                       |

|------|-------------------------------------------------|

| 1-2  | Current Requirements (Amps) 1-6                 |

| 1-3  | Total Module Requirements (Watt)                |

| 2-1  | Starting Address Switches 2-7                   |

| 2-2  | CSR Switches 2-8                                |

| 2-3  | MS11-P Pin Allocation (M8743) 2-9               |

| 2-4  | Read, No Errors 2-19                            |

| 2-5  | Read, Single Error 2-20                         |

| 2-6  | Read, Double Error 2-21                         |

| 2-7  | Write Cycle 2-22                                |

| 2-8  | Byte Write, No Errors Detected During Read 2-23 |

| 2-9  | Byte Write, Single Error Detected During        |

|      | Read                                            |

| 2-10 | Byte Write, Double Error Detected During        |

|      | Read                                            |

| 3-1  | 16-Bit Modified Hamming Code Check Bit          |

|      | Encode Chart 3-11                               |

| 3-2  | Syndrome Decode to Bit-in-Error                 |

| 3-3  | CSR Cycle Selection 3-15                        |

| 3-4  | Error Register Operation 3-16                   |

| 3-5  | Multiplexer Control 3-16                        |

| 3-6  | Address Decoder ROM Outputs 3-20                |

| 3-7  | UNIBUS Cycle Control                            |

| 3-8  | Initial Microsequencer Address 3-27             |

| 3-9  | Location 14A Contents 3-27                      |

| 3-10 | Location 34 Contents 3-29                       |

| 3-11 | Location 35 Contents 3-29                       |

| 3-12 | Location 36 Contents 3-29                       |

| 3-13 | Location 37 Contents 3-29                       |

| 3-14 | Location Ø Contents 3-29                        |

|      |                                                 |

4

¢,

C

# CHARACTERISTICS AND SPECIFICATIONS

#### 1.1 INTRODUCTION

The MSll-PB (M8743-BA) is a metal oxide semiconductor (MOS), random access memory (RAM), which provides 512K X 16 bits of data storage. The MSll-PB is designed for use with the PDP-11 extended UNIBUS. (This memory is four times larger than the UNIBUS address space.) The memory is a slave device to the PDP-11 processor, or to any peripheral device designated bus master. The MSll-P protects its data with error correction code (ECC) bits, which increase memory reliability.

#### 1.2 GENERAL DESCRIPTION

The MS11-P consists of a single hex-height module (M8743-BA) which contains the extended UNIBUS interface, timing and control logic, error correcting code (ECC) logic, and a MOS storage array. The module also contains circuitry for ECC initialization and memory refresh, and a control and status register (CSR).

You can set the memory starting address at any 8K boundary within the 2048K extended UNIBUS address space. (The extended UNIBUS contains 22 address lines as opposed to 18 UNIBUS address lines.) The MS11-P reserves the top 128K of the extended UNIBUS address space for the I/O peripheral page.

The MOS storage array is configured in 22-bit words, which consist of a 16-bit PDP-11 word and six check bits generated by the ECC logic. The error correction code allows the MS11-P to detect a single-bit or double-bit error within the 22-bit word, and to correct a single-bit data error. The MS11-P does not correct a double-bit error, but can be configured to cause a parity error trap on a double-bit error. A single-bit error is transparent to the extended UNIBUS.

The memory storage elements are 65536 X l bit, MOS dynamic RAM devices. The MOS storage array contains 22 of these devices for each 64K bank of PDP-11 memory. Therefore, a memory module contains 176 storage devices. The MS11-P executes specially timed refresh cycles that periodically refresh the MOS storage devices. This ensures that data and check bits remain valid.

1-1

MOS storage devices are volatile (data is not retained when power is lost), so DIGITAL provides an optional battery backup unit to support the MOS power supply regulator(s). Therefore, during an ac power failure, dc power is available to MOS memory for a limited time only. The MS11-P memory module has inputs for two sources of +5 V power. These inputs are designated +5 VBB and +5 V. The +5 VBB module input is battery supported during an ac power failure; the +5 V input is not battery supported. The power distribution lines on the module are arranged to accommodate use of the battery backup option. In battery support mode, power is used only to refresh the MOS storage array so that battery backup time, and therefore data retention time, is maximized. A green LED on the module stays on as long as power is applied to the +5 VBB input.

If +5 VBB (and therefore data) is lost during an ac power failure, the MS11-P performs an error correction initialize (ECC INIT) operation after the power-up. For an ECC INIT operation, logical .0s and the corresponding check bit pattern are written into all 22-bit word locations in the MOS storage array. Signal AC LO is asserted by memory while ECC INIT is in progress.

The control and status register (CSR) in the MS11-P allows program control of certain ECC functions, and stores diagnostic information if an error has occurred. The CSR has its own address in the I/O peripheral page, and can be read or written into by any device designated as bus master.

Although the MOS storage array is configured in 22-bit words, the bus master sees the MS11-P as a standard 16-bit memory. The following paragraphs describe the memory response to the four types of data transfers (DATI, DATIP, DATO, and DATOB).

# 1.2.1 DATI or DATIP Data Transfer

Memory responds to a DATI or DATIP data transfer by performing a read cycle. (Memory interprets a DATIP data transfer as a DATI.) Memory retrieves the 22-bit word, that contains the requested data, from the MOS storage array, and calculates 6 check bits based on the 16 retrieved data bits. Then, memory compares the newly calculated check bits to the six retrieved check bits, which creates six syndrome bits. A logical 1 in the syndrome bit pattern indicates an error in the 22-bit word; an odd number of logical 1s indicates a single-bit error, while an even number of logical 1s indicates a double-bit error. If no error is detected, memory places the requested 16-bit data on the extended UNIBUS, and asserts the SSYN signal. If a single-bit error is detected during a read cycle, the MS11-P initiates the following action.

- 1. A single-bit error within the 16 data bits is corrected.

- 2. Bit 4 in the CSR is set to 1.

- 3. A partial address of the requested data is recorded in the CSR, if CSR bit 15 is cleared to Ø.

- 4. The syndrome bits are logged in the CSR.

- 5. The requested 16-bit data and the SSYN signal are asserted on the extended UNIBUS after approximately a 230 ns delay. Therefore, the memory access time is increased due to a single-bit error.

Note that the syndrome bits determine if the single-bit error is contained in the retrieved data or check bits, and isolate a bad data bit. A check bit error is not corrected; however, the other single-bit error reactions are the same.

If a double-bit error is detected it is not corrected. However, the memory initiates the following actions.

- 1. Bit 15 in the CSR is set to 1.

- 2. A red LED on the module turns on, which indicates a double-bit (uncorrectable) error.

- 3. A partial address of requested data, pointing to a 1K block of memory, is recorded in the CSR. Any address information that relates to a previous error is destroyed. No future single bit error can record address information until the CSR is cleared.

- 4. The syndrome bits are logged in the CSR.

- 5. If bit zero in the CSR is set, the memory asserts BUS PBL which warns the processor that a double-bit (uncorrectable) error has occurred.

- 6. The requested 16-bit data and the SSYN signal are asserted on the extended UNIBUS after approximately a 230 ns delay. Therefore, the memory access time is increased due to a double-bit error.

#### **1.2.2** DATO Data Transfer

Memory responds to a DATO data transfer by performing a write cycle. The data supplied by the bus master is latched-in from the extended UNIBUS. Memory calculates six checks bits, and then writes all 22 bits into the specified location.

#### 1.2.3 DATOB Data Transfer

Memory responds to a DATOB data transfer by performing an internal read modify write (RMW) cycle. During the first portion of the RMW cycle, the data byte supplied by the bus master is latched-in from the extended UNIBUS, and the SSYN signal is asserted. The 22-bit word, which includes the specified byte, is then retrieved from the MOS storage array. Based on the 16 retrieved data bits, memory calculates 6 check bits and then compares them to the retrieved check bits, which creates 6 syndrome bits. The syndrome bits are examined to determine if the 22-bit word contains a single-bit or double-bit error. A single-bit error in the data is corrected, but a double-bit error in the 22-bit word is not corrected.

Data manipulation during the remainder of the RMW cycle is the same for a no error or corrected error condition. The 22-bit word is modified by merging the data byte supplied by the bus master, with the old data bytes from the storage array. Check bits are generated based on both data bytes, and the modified 22-bit word is then written into the MOS storage array.

If a double-bit error is detected during the first part of the RMW cycle, the old data and the old check bits are rewritten into the MOS storage array. Therefore, the double-bit error is preserved and will be flagged if the 22-bit word is retrieved during a DATI or DATIP data transfer. The data supplied by the bus master is lost.

#### 1.3 SPECIFICATIONS

The following paragraphs contain MS11-P MOS memory specifications.

# **1.3.1** Functional Specifications

| Capacity MS11-PB 524288 (512K) | 16-bit PDP-11 words                                                            |

|--------------------------------|--------------------------------------------------------------------------------|

| Refresh timing Cycle time      | 675 ns (typical),<br>725 ns (maximum)                                          |

| Repetition rate                | One cycle every:<br>13.3 u (typical)<br>11.25 u (fastest)<br>13.75 u (slowest) |

NOTE

Refresh cycle time is the time interval between the assertion of REF REQ L and the negation of BUSY L. These signals are internal to the memory module.

#### NOTE

ECC INIT time is the time interval between the negation of DC LO (at the memory receiver output) and the negation of AC LO (on the extended UNIBUS) by memory.

Access and Cycle times (Table 1-1)

#### NOTE

Access time is the time interval between memory reception of MSYN (at the bus receiver's input) and the assertion of SSYN on the UNIBUS.

Cycle time is the interval between memory reception of MSYN (at the bus receiver's output) when memory is not busy, and the negation of BUSY L.

| Table | 1-1 | Access | and | Cycle | Times |

|-------|-----|--------|-----|-------|-------|

|       |     |        |     |       |       |

| Data Transfer |          | Access Time<br>Typical | (ns)<br>Maximum    | Cycle Time (ns)<br>Typical Maxim |      |  |

|---------------|----------|------------------------|--------------------|----------------------------------|------|--|

| DATI/DATIP    | (memory) | 490<br>(720 w/err)     | 535<br>(750 w/err) | 68Ø                              | 75Ø  |  |

| DATO          | (memory) | 100                    | 125                | 58Ø                              | 620  |  |

| DATOB         | (memory) |                        |                    | 1100                             | 115Ø |  |

| DATI/DATIP    | (CSR)    |                        | 53Ø                |                                  |      |  |

| DATO          | (CSR)    |                        | 220                |                                  |      |  |

# 1.3.2 Electrical Specifications

Voltage requirements +5 V +5%, maximum ripple = 0.2 V

peak-to-peak

+5 VBB +5%, maximum ripple = 0.2 V

peak-to-peak

Current and power (Refer to Tables 1-2 and 1-3)

requirements NOTE

The total module consumption of +5 V current during normal operation is equal to the sum of the +5 V and +5 VBB ratings.

Table 1-2 Current Requirements (Amps)

|                          | Typical | Maximum |

|--------------------------|---------|---------|

| +5 V                     | 3.4 A   | 4.8 A   |

| +5 <b>V</b> BB<br>Active | 2.Ø A   | 2.8 A   |

| +5 VBB<br>Standby        | 1.7 A   | 2.4 A   |

Table 1-3 Total Module Power Requirements (Watts)

|                | Typical | Maximum |  |

|----------------|---------|---------|--|

| Active         | 27. W   | 38 W    |  |

| Standby        | 25.5 W  | 36 W    |  |

| Battery Backup | 8.5 W   | 12 W    |  |

٤,

Physical and Environmental Specifications 1.3.3 M8743-BA Module designation MS11-PB 21.6 X 38.1 cm (8.5 X 15 in) Hex-height multilayer  $5^{\circ}$  to  $50^{\circ}$  C (41° to 122° F) Operating temperature 10 to 95% (noncondensing) Humidity 1.4 RELATED DOCUMENTS You can find more reference information in the following documents. Title Document Number MS11-P Field Maintenance Print Set MP-01477 PDP-11 Peripherals Handbook EB-05961 PDP-11/04/24/34a/44/70 Processor Handbook EB-19402-20 PDP-11/44 System User's Guide EK-11044-UG EK-KD117-TMPDP-11/44 System Technical Manual You can order these documents from: Digital Equipment Corporation 444 Whitney Street Northboro, MA Ø1532 Attn: Communication Services (NR2/M15) Customer Services Section For information about Microfiche Libraries, contact: Digital Equipment Corporation Micropublishing Group BU/D2 12 Crosby Drive Bedford, MA Ø1730

Q

#### CHAPTER 2 INSTALLATION AND PROGRAMMING

#### 2.1 GENERAL

This chapter provides the information necessary to install and program the MS11-P. Installation procedures include switch/jumper settings, backplane placement, power voltage checks, and MAINDEC testing. Programming information includes a discussion of bit assignments in the control and status register (CSR).

#### **2.**2 INSTALLATION

Before you remove or replace an MS11-P memory module, exercise the following cautions.

#### CAUTION

Static charges can damage the MOS memory chips. Be careful how you handle the module and where you lay it down.

We recommend that you use an antistatic wrist strap when removing or replacing the MS11-P memory module. DIGITAL offers a wrist-strap kit, PN A2-M-Ø299-1Ø (Appendix A).

When you install or remove a memory module, make sure there is no dc voltage applied to the module.

If the green LED is on, the module is receiving +5 V from the power supply or battery backup. The power source must be off before you remove or replace a memory module.

#### 2.2.1 Switch and Jumper Configurations

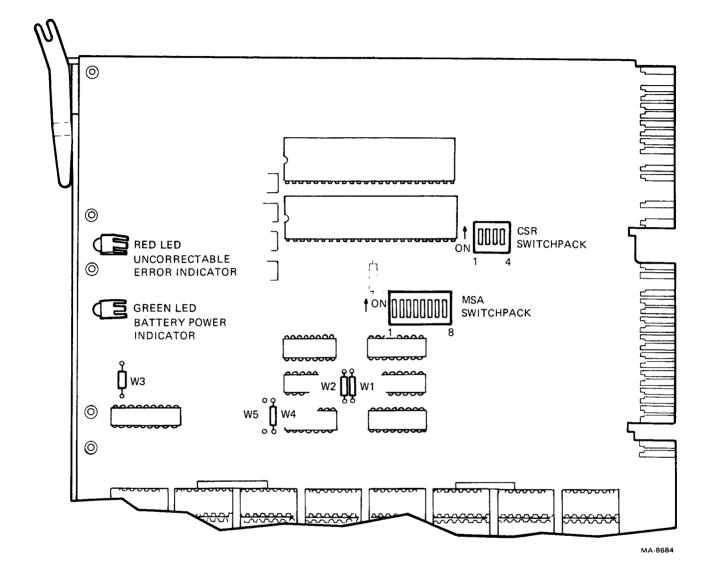

The MS11-P contains two switchpacks and five jumpers. One switchpack contains four switches (S1-1 through S1-4) and the other contains eight switches (S2-1 through S2-8). Figure 2-1 shows the switch and jumper locations1. The switches specify the memory starting address and the CSR address. The jumpers are factory set and should not be changed in the field.

Figure 2-1 Switch and Jumper Locations

٠.

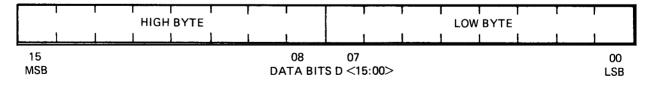

2.2.1.1 Memory Addressing -- PDP-11 Memory Conventions -- The MS11-P is designed for use with the PDP-11 extended UNIBUS (EUB). Memory in these computer systems provides storage for 16-bit data words, each of which contains two 8-bit bytes. These bytes are identified as low or high (Figure 2-2).

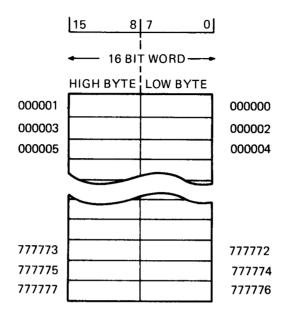

Each byte is addressable and has its own address location; low bytes are even numbered and high bytes are odd numbered. Words are addressed by even numbered locations only, and the high (odd) byte for each word is automatically included.

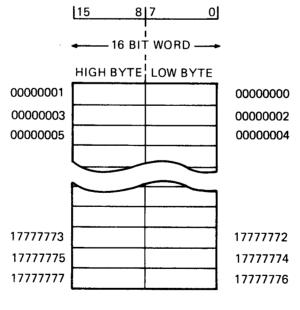

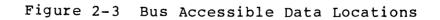

Via the UNIBUS, 131,072 (128K) words or 262,144 (256K) bytes can be addressed. Via the extended UNIBUS, 2,097,152 (2048K) words or 4,194,034 (4096K) bytes can be addressed. A six-digit octal number specifies each byte location in UNIBUS memory. However, with the extended UNIBUS, an eight-digit octal number specifies each byte location. The address range is 000000--777777 on the UNIBUS and 00000000--17777777 on the extended UNIBUS (Figure 2-3).

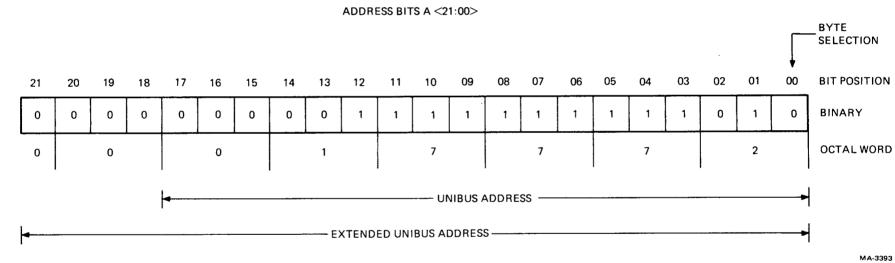

Memory address decoding logic responds to the binary equivalent of the octal address. Figure 2-4 shows the binary equivalent of 00017772. The MS11-P decodes a 22-bit address (A21 -- A00) on the extended UNIBUS.

The memory starting address and storage capacity determine the address space on a bus occupied by a memory module. Switches on the MS11-P that correspond to address bits A21 -- A14 on the extended UNIBUS select a unique starting address. The block of addresses occupied by each module is continuous.

Memory Starting Address Selection -- The memory starting address (MSA) is the lowest bus address to which the MS11-P responds. You must assign the starting address to an 8K boundary within the 2048K extended UNIBUS address space. If you are adding memory to a system, find out how much memory the system has before you install the new memory module. That size is the added memory's starting address.

MA-2458

Figure 2-2 PDP-11 Data Word

2-3

#### UNIBUS ADDRESS SPACE

# EXTENDED UNIBUS ADDRESS SPACE

MA-3392

U

٠

.

•

+

¢

You assign the starting address by manually setting eight switches, S2-1 through S2-8, to the appropriate positions for the desired location. A switch in the off position corresponds to a logical one. Switches S2-1 through S2-3 correspond to address bits A21 -- A19 on the extended UNIBUS. Table 2-1 lists two groups of addresses. The first group of eight addresses is in increments of 256K decimal words which correspond to address bits A21 -- A19 (EUB). The second group of 32 addresses is in 8K decimal word increments which correspond to address bits A18 -- A14 (UNIBUS).

Determine the MSA switch settings for an MSA of 376K decimal words.

1. Find the 256K increment of the MSA.

Table 2-1 lists the 256K increment as EUB address group 1. The switch column shows that S1 through S2 are closed and S3 is open.

2. Find the 8K increment of the MSA.

Subtract the number in EUB group 1 (256K) from the MSA (376K). The result is 120K. Table 2-1 lists the 120K increment as UNIBUS group 15. The switch column shows that S4 is closed and S5 through S8 are open.

2.2.1.2 CSR Address Selection -- Address decoding logic in the MS11-P specifies the control and status register (CSR) address in the 17772100--17772136 range. Four switches, S1-1 through S1-4, select the CSR address. Switches S1-1 through S1-4 correspond to address bits A04 -- A01 respectively; a switch in the off position corresponds to a logical one. The CSR is always accessed as an entire data word, since bit A00 is not decoded by the CSR address logic.

The CSR address does not affect the MS11-P's memory starting address or storage capacity. However, it helps to assign CSR addresses to modules in the same order as the memory starting addresses. Each memory module's CSR is assigned a specific address. The memory module closest to the CPU is called module number 1. Table 2-2 shows that CSR switches selected for module one (CSR address 17772100) are all closed.

The next sequential CSR address is for memory module number 2 and so on, until CSR number 16 is reached. CSR 16 is the last reserved CSR address location.

| EUB<br>Group | Decimal K<br>Words | Octal K<br>Word        | <b>S</b> 1 | S2     | <b>S</b> 3 | S4     | S5     | S6     | s7     | S 8        |

|--------------|--------------------|------------------------|------------|--------|------------|--------|--------|--------|--------|------------|

| Ø            | ØØØØ               | 0000 0000              | с          | С      | С          |        |        |        |        |            |

| 1            | 256                | 0200 0000              | С          | С      | 0          |        |        |        |        |            |

| 2            | 512                | 0400 0000              | С          | 0      | C          |        |        |        |        |            |

| 3            | 768<br>1Ø24        | 0600 0000<br>1000 0000 | С          | 0      | 0          |        |        |        |        |            |

| 4<br>5       | 1024<br>1280       | 1200 0000              | 0<br>0     | C<br>C | C<br>O     |        |        |        |        |            |

| 6            | 1536               | 1400 0000              | 0          | 0      | c          |        |        |        |        |            |

| 7            | 1792               | 1600 0000              | õ          | õ      | 0          |        |        |        |        |            |

| UNIBUS       | Decimal K<br>Words | Octal K<br>Word        | <b>S</b> 1 | S2     | <b>S</b> 3 | S4     | S5     | S6     | S7     | <b>C</b> 0 |

| Group        | WOLUS              | WOLU                   | 51         | 52     | 55         |        | 35     | 50     |        | <u> </u>   |

| Ø            | Ø                  | 0000 0000              |            |        |            | С      | С      | С      | С      | С          |

| 1            | 8                  | 0004 0000              |            |        |            | С      | С      | С      | С      | 0          |

| 2            | 16                 | 0010 0000              |            |        |            | C      | C      | C      | 0      | C          |

| 3<br>4       | 24<br>32           | 0014 0000<br>0020 0000 |            |        |            | C<br>C | C<br>C | C<br>O | 0<br>C | 0          |

| 4<br>5       | 52<br>4Ø           | 0020 0000<br>0024 0000 |            |        |            | c      | c      | 0      | c      | C<br>O     |

| 6            | 48                 | 0024 0000<br>0030 0000 |            |        |            | c      | c      | 0      | 0      | C          |

| 7            | 56                 | ØØ34 ØØØØ              |            |        |            | č      | č      | ŏ      | õ      | õ          |

| 8            | 64                 | 0040 0000              |            |        |            | Ċ      | 0      | Ċ      | Č      | Ċ          |

| 9            | 72                 | ØØ44 ØØØØ              |            |        |            | С      | 0      | С      | С      | 0          |

| 10           | 8Ø                 | ØØ5Ø ØØØØ              |            |        |            | С      | 0      | С      | 0      | С          |

| 11           | 88                 | 0054 0000              |            |        |            | С      | 0      | С      | 0      | 0          |

| 12           | 96                 | 0060 0000              |            |        |            | C      | 0      | 0      | C      | С          |

| 13           | 104                | ØØ64 ØØØØ<br>8864 8888 |            |        |            | С      | 0      | 0      | C      | 0          |

| 14<br>15     | 112<br>12Ø         | 0064 0000<br>0074 0000 |            |        |            | C<br>C | 0<br>0 | 0<br>0 | 0<br>0 | C<br>O     |

| 16           | 128                | 0100 0000<br>0100 0000 |            |        |            | 0      | c      | c      | c      | c          |

| 17           | 136                | 0100 0000              |            |        |            | õ      | c      | c      | C      | õ          |

| 18           | 144                | 0110 0000              |            |        |            | Ō      | Č      | Ċ      | Ō      | Č          |

| 19           | 156                | Ø114 ØØØØ              |            |        |            | 0      | С      | С      | 0      | 0          |

| 2Ø           | 160                | 0120 0000              |            |        |            | 0      | С      | 0      | С      | С          |

| 21           | 168                | 0124 0000              |            |        |            | 0      | С      | 0      | С      | 0          |

| 22           | 176                | 0130 0000              |            |        |            | 0      | С      | 0      | 0      | С          |

| 23           | 184                | Ø134 ØØØØ              |            |        |            | 0      | C      | 0      | 0      | 0          |

| 24           | 192<br>200         | 0140 0000<br>0144 0000 |            |        |            | 0<br>0 | 0<br>0 | C<br>C | C<br>C | C          |

| 25<br>26     | 200<br>208         | 0144 0000<br>0150 0000 |            |        |            | 0      | 0      | c      | 0      | 0<br>C     |

| 20           | 208                | Ø154 ØØØØ              |            |        |            | 0      | 0      | c      | 0      | 0          |

| 28           | 224                | 0160 0000              |            |        |            | ŏ      | ŏ      | õ      | č      | č          |

| 29           | 232                | Ø164 ØØØØ              |            |        |            | õ      | õ      | Õ      | Ĉ      | 0          |

| 30           | 240                | 0170 0000              |            |        |            | 0      | 0      | 0      | 0      | 0<br>C     |

| 31           | 248                | 0174 0000              |            |        |            | 0      | 0      | 0      | 0      | 0          |

| Table 2 | 2-1 | Starting | Address | Switches |

|---------|-----|----------|---------|----------|

|---------|-----|----------|---------|----------|

·

Table Switch Settings

C = closed (on)0 = open (off)

| CSR Module |                | LSB |    |    | MSB |

|------------|----------------|-----|----|----|-----|

| Number     | UNIBUS Address | A1  | A2 | A3 | A4  |

| 1          | 17772100       | С   | С  | С  | С   |

| 2          | 17772102       | 0   | С  | С  | С   |

| 3          | 17772104       | С   | 0  | С  | С   |

| 4          | 17772106       | 0   | 0  | С  | С   |

| 5          | 17772110       | С   | С  | 0  | С   |

| 6          | 17772112       | 0   | С  | 0  | С   |

| 7          | 17772114       | С   | 0  | 0  | С   |

| 8          | 17772116       | 0   | 0  | 0  | С   |

| 9          | 17772120       | С   | С  | С  | 0   |

| 10         | 17772122       | 0   | С  | С  | 0   |

| 11         | 17772124       | С   | 0  | С  | 0   |

| 12         | 17772126       | 0   | 0  | С  | 0   |

| 13         | 17772130       | С   | С  | 0  | 0   |

| 14         | 17772132       | 0   | С  | 0  | 0   |

| 15         | 17772134       | С   | 0  | 0  | 0   |

| 16         | 17772136       | 0   | 0  | 0  | 0   |

Table 2-2 CSR Switches

Table Switch Settings

C = closed (on)0 = open (off)

#### 2.2.2 Backplane Placement

The MS11-P is compatible with the PDP-11 extended UNIBUS (EUB), which is the main memory bus in the PDP-11/44.

When used with the PDP-11/44, the MS11-P should be inserted into any one of slots 9 through 12 in the processor backplane (PN 70-16502-00). Slots 9 through 12, sections A and B, contain the extended UNIBUS.

When used with the PDP-11/24, the MS11-P should be inserted into any one of slots 3 through 6 in the processor backplane. Slot 2 should hold the KT24 UNIBUS MAP option (M7134) to properly use the MS11-P capacity.

Table 2-3 shows the MS11-P backplane connections.

#### 2.2.3 Power Voltage Check

Once primary power is on, you should check the following dc power voltages at the backplane.

| Voltage and Tolerance | Backplane Pin |

|-----------------------|---------------|

| +5 V +5%              | AA2, BA2, CA2 |

| +5 VBB +5%            | BB1, BD1      |

|   | A         |              | В          |            | С                |   | D |              |   | Е |     |   | F |     |

|---|-----------|--------------|------------|------------|------------------|---|---|--------------|---|---|-----|---|---|-----|

|   | 1         | 2            | 1          | 2          | 1 2              | 1 |   | 2            | 1 |   | 2   | 1 |   | 2   |

| A | INIT<br>L | +5V          |            | +5V        | NPG 7+5V<br>IN H |   |   | +5V          |   |   | +5V |   |   | +5V |

| В |           | BOOT<br>EN L | +5V<br>BAT |            | NPG<br>OUT H     |   |   |              |   |   |     |   |   |     |

| С | DØØ<br>L  | GND          |            | GND        | GND              |   |   | GND          |   |   | GND |   |   | GND |

| D | DØ2<br>L  | DØ1<br>L     | +5V<br>BAT |            |                  |   |   |              |   |   |     | - |   |     |

| Ē | DØ4<br>L  | DØ3<br>L     | A19<br>L   | A18<br>L   |                  |   |   |              |   |   |     |   |   |     |

| F | DØ6<br>L  | DØ5<br>L     | AC<br>LO L | DC<br>LO L |                  |   |   |              |   |   |     |   |   |     |

| Н | DØ8<br>L  | DØ7<br>L     | AØ1<br>L   | AØØ<br>L   |                  |   |   |              |   |   |     |   |   |     |

| J | DlØ<br>L  | DØ9<br>L     | AØ3<br>L   | AØ2<br>L   |                  |   |   |              |   |   |     |   |   |     |

| К | D12<br>L  | D11<br>L     | AØ5<br>L   | AØ4<br>L   |                  |   |   | BG7<br>SO H  |   |   |     |   |   |     |

| L | D14<br>L  | D13<br>L     | AØ7<br>L   | AØ6<br>L   |                  |   |   | BG7<br>OUT H |   |   |     |   |   |     |

r

Table 2-3 MS11-P Pin Allocation (M8743)

6

r

|   | A        |          | В         |          | С   |   | D                 |              | E   |   | F   |   |

|---|----------|----------|-----------|----------|-----|---|-------------------|--------------|-----|---|-----|---|

|   | 1        | 2        | 1         | 2        | 1   | 2 | 1                 | 2            | 1   | 2 | 1   | 2 |

| м |          | D15<br>L | AØ9<br>L  | AØ8<br>L |     |   |                   | BG6<br>SO H  | ]   |   |     |   |

| N | A21<br>L | PB<br>L  | All<br>L  | AlØ<br>L |     |   |                   | BG6<br>OUT H | ,   |   |     |   |

| Ρ | A2Ø<br>L |          | Al3<br>L  | Al2<br>L |     |   |                   | BG5<br>SO H  | ]   |   |     |   |

| R |          |          | Al5<br>L  | Al4<br>L |     |   |                   | BG5<br>OUT H |     |   |     |   |

| S |          |          | A17<br>L  | A16<br>L |     |   | INH<br>REFL<br>TP | BG4<br>SO H  |     |   |     |   |

| т | GND      |          | GND       | Cl<br>L  | GND |   | GND               | BG4<br>OUT H | GND |   | GND |   |

| U |          |          | SSYN<br>L | CO<br>L  |     |   |                   |              |     |   |     |   |

| V |          |          | MSYN<br>L |          |     |   |                   |              |     |   |     |   |

Table 2-3 MS11-P Pin Allocation (M8743) (Cont)

NOTE: Pins marked by a bracket are tied together on the module to provide grant continuity.

C

1.

4

1

#### 2.2.4 MAINDEC Testing

You should use the MS11-L/M/P Memory Exerciser (MAINDEC-11-CZMSPA) diagnostic program with the MS11-P memory module. To check correct memory operation, follow the procedure described in Paragraph 2.2.4.1. No double errors are permitted. Also, make sure the program printout confirms the total memory in the system.

#### 2.2.4.1 Test Procedure

Do the following steps to test correct memory operation.

- 1. Set the starting address and CSR address for each MS11-P according to Paragraph 2.2.1.

- 2. Run the CZMSPA diagnostic. (Refer to the printout example.) Run two passes. The first pass defaults to a quick verification (QV).

- 3. If four MS11-Ps are installed, follow the same procedure as above; but, after the diagnostic pass for all four modules, do the following extra steps.

- a. Remove the modules with the lowest and highest starting addresses. Reset the switch settings on the modules so their starting addresses are swapped. Reinstall the two modules in the backplane. Do this because the diagnostic cannot test the upper 128K of the highest address module, since this memory space is reserved for the I/O page.

- b. Start the diagnostic again and run one pass. Run the diagnostic until the lowest addressed module has been tested. One pass in the QV mode will take eight minutes.

- 4. All the diagnostic passes should be error-free.

Following these four steps helps you make sure all memory is installed successfully.

NOTE Paragraph 4.3.6 is a simplified toggle-in memory test.

\*\*\* TEST DISPLAY PRINTOUT \*\*\* >>>b dx0 CHMDXB1 XXDP+ DX MONITOR BOOTED VIA UNIT Ø 28K UNIBUS SYSTEM ENTER DATE (DD-MMM-YY): RESTART ADDR: 152010 THIS IS XXDP+. TYPE "H" OR "H/L" FOR HELP. r zmsp?? CZMSPA MS11-L/M/P MEMORY DIAGNOSTIC 11/44 CACHE AVAILABLE CSR MAP CSR Ø 1 2 3 4 5 6 7 8 9 A B C D E F MEMTYPE P 512K OF MS11-P 512K WORDS OF MEMORY TOTAL MEMORY CONFIGURATION MAP 16K WORD BANKS 3 5 7 2 4 6 1 01234567012345670123456701234567012345670123456701234567012345670123 ERRORS INTRLV МЕМТҮРЕ РРРРРРРРРРРРРРРРРРРРРРРРРРРРРРРРР CSR PROTECT PP BANK= 10 TEST=31 BANK= 13 TEST=33 Optional display with CTRL/T BANK= 16 TEST=33 BANK= 21 TEST=24 BANK= 24 TEST=24BANK= 30 TEST=33 END PASS #QV 1 END PASS # 2

#### 2.3 CSR BIT ASSIGNMENT

the same time as data.

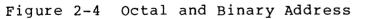

The control and status register (CSR) in the MS11-P allows program control of certain ECC functions, and contains diagnostic information if an error has occurred. The CSR has an assigned address and can be accessed by a bus master via the extended UNIBUS. The assertion of BUS INIT L clears some CSR bits. BUS INIT L is asserted for a short time after system power has come up, or in response to a reset instruction. Figure 2-5 shows the CSR bit assignments described in Paragraph 2.3.1 through 2.3.9. Note that all unused bits are read as zero. Paragraphs 2.3.10 and 2.3.11 give more detailed CSR usage information.

2.3.1 Uncorrectable Error Indication Enable (Bit  $\emptyset$ ) If a double error occurs with ECC enabled, or a single or double error occurs with ECC disabled and bit  $\emptyset$  set, then during a DATI or DATIP cycle to memory, BUS PB L is asserted on the UNIBUS at

This is a read/write bit reset to zero on power up or BUS INIT.

#### 2.3.2 Disable Correction Mode (Bit 1)

This bit is a diagnostic aid which allows reading data from memory without interference from error correction circuitry. When bit 1 is set, no single errors are corrected. A single error sets CSR bit 4 and CSR bit 15, and a double error sets CSR bit 15.

This is a read/write bit reset to zero on power up or BUS INIT.

2.3.3 Diagnostic Check Mode (Bit 2) This bit is a diagnostic aid which allows reading or writing the

check bits at a given memory location. Bit 2 also allows reading the error syndromes after a single or double error.

Example 1 shows how to write check bits to a memory location.

Example 1

- Write the desired check bits into CSR bits 5 through 10, and enable diagnostic check mode.

- A subsequent DATO or DATOB to memory writes the check bits stored in CSR bits 5 through 10 to the check bit RAMs.

Example 2 shows how to examine the check bits at a memory location.

Example 2

- Write the CSR to enable diagnostic check mode.

- A subsequent DATI or DATIP to memory reads the check bits stored in memory and clocks them into CSR bits 5 through 10. The check bits can then be examined by reading the CSR.

| 15<br>14<br>13 | Uncorrectabl<br>error<br>EUB error<br>Address retr<br>Set inhibit<br>mode | ieval  |                    |     |      |     |                          |     |     |   |                        |

|----------------|---------------------------------------------------------------------------|--------|--------------------|-----|------|-----|--------------------------|-----|-----|---|------------------------|

| 12             | Reserved (al                                                              | ways r | ead as ze          | ro) |      |     |                          |     |     |   |                        |

| 11             | A17                                                                       | Ø      |                    | 1   | if b | its | 2, 13, 14                | = 1 |     |   |                        |

| 10             | A16                                                                       | Ø      |                    | Ck  | bit  | 8   |                          | Syn | bit | 8 |                        |

| 9              | Al5 Error<br>address                                                      | Ø      | Error<br>address   | Ck  | bit  | 4   | Diag chk<br>mode only    | Syn | bit | 4 | Loaded<br>only when    |

| 8              | Al4 Read<br>when                                                          | A21    | Read<br>when       | Ck  | bit  | 2   | -                        | Syn | bit | 2 | there is<br>a single   |

| 7              | Al3 CSR14=Ø<br>or                                                         | A 2 Ø  | CSR14=1<br>or      | Ck  | bit  | 1   | memory<br>read or        | Syn | bit | 1 | or double<br>error and |

| 6              | A12 CSR15=1<br>or                                                         | A19    | CSR15=1<br>or      | Ck  | bit  | Ø   |                          | Syn | bit | Ø |                        |

| 5              | All CSR14=Ø<br>CSRØ4=1                                                    | A18    | CSR14=1<br>CSRØ4=1 | Ck  | bit  | Х   | write<br>with<br>CSRØ2=1 | Syn | bit | Х | when<br>CSRØ2=1        |

| 4              | Single                                                                    |        |                    |     |      |     | CSR02-1                  |     |     |   |                        |

|                | error                                                                     |        |                    |     |      |     |                          |     |     |   |                        |

| 3              | Inhibit mode                                                              |        | -                  |     |      |     | Used wit                 | t h |     |   |                        |

| 2              | pointer l protects 2nd 16K CSR 13<br>Diagnostic                           |        |                    |     |      |     |                          |     |     |   |                        |

| 1              | check<br>Disable correction<br>mode                                       |        |                    |     |      |     |                          |     |     |   |                        |

| Ø              | Uncorrectable<br>indication er                                            |        | r                  |     |      |     |                          |     |     |   |                        |

.

\*

If a single or double error occurs during normal memory operation, the SERR or DERR bit respectively in the CSR is set, and the error syndrome bits and error address bits are stored in CSR bits 5 through 11. In diagnostic check mode, the error syndrome bits are read when CSR bits 10 through 5 are read.

This bit is a read/write bit reset on power up or BUS INIT.

#### 2.3.4 Inhibit Mode Pointer (Bit 3)

This bit works in conjunction with set inhibit mode (bit 13). When bit 13 is set to 1, a 16K portion of memory is inhibited from operating in disable correction mode or diagnostic check mode.

The inhibit mode pointer indicates which 16K is being inhibited. For example, if bit 3 equals  $\emptyset$ , the first 16K of memory is inhibited, and if bit 3 equals 1, the second 16K of memory is inhibited.

If bit 13 is set to  $\emptyset$ , this bit has no effect.

Therefore bit 3, in conjunction with bit 13, allows a 16K portion of memory to always have ECC coverage. The systems diagnostic can reside in this protected portion of memory and disable error correction, and/or run diagnostic check mode in the rest of memory without itself becoming vulnerable to single errors.

This bit is a read/write bit reset by power up and BUS INIT.

2.3.5 Single Error (Bit 4) If a single bit error is detected on a DATI or DATIP cycle, bit 4 is set.

During normal operation, when a single bit error is detected, the error address and syndromes are logged in CSR bits 5 through 11 (unless uncorrectable error CSR bit 15 is set). The error address and syndromes are logged unconditionally in the disable correction mode.

If a single bit error is detected on a DATI or DATIP cycle to memory while in DIAG CHECK mode, CSR bit 4 is set, but the error address and syndromes are not logged in the CSR.

This bit is a read/write bit reset by power up or BUS INIT.

2.3.6 Error Address and Check Bit Storage (Bits 5 -- 11)

2.3.6.1 Check Bit Storage (Diagnostic Check Bit 2 = 1, Disable Correction Bit 1 = Do Not Care) -- These bits are read/write bits in diagnostic check mode. They store the check bits to be written into, or read from, memory.

A one is read in CSR bit 11 if CSR bits 2, 13, and 14 are set to indicate that the memory under test is an MS11-P.

2.3.6.2 UNIBUS Address Storage (Diagnostic Check Bit  $2 = \emptyset$ , Disable Correction Bit 1 = Do Not Care) -- These bits store address bits All through Al7 if a double or single error occurs on a DATI or DATIP cycle.

2.3.6.3 EUB Address Storage (Diagnostic Check Bit  $2 = \emptyset$ , Disable Correction Bit 1 = Do Not Care) -- If a double or single error occurs on a DATI or DATIP cycle, address bits Al7 through All are stored in CSR bits 11 through 5, and address bits A21 through Al8 are stored in a backup register. The EUB error address retrieval bit (CSR bit 14) is used to obtain the total error address as follows.

When CSR bit 14 equals  $\emptyset$ , a read to the CSR obtains A17 through All from CSR bits 11 through 5.

CSR bit 14 is now written to a one, and a read to the CSR then reads A21 through A18 from CSR bits 8 through 5, and zeros from CSR bits 11 through 9.

Address bits A21 through All are therefore obtained to locate the double error to a 1K portion of memory.

The EUB address A21 through A18 is read only when CSR 14 equals 1.

**2.3.6.4** Syndrome Storage -- If, during normal operation, a double or single error occurs during a DATI, DATIP, or DATOB cycle, and if CSR bit 2 is set to  $\emptyset$ , CSR bits 5 through 1 $\emptyset$  store syndrome bits X,  $\emptyset$ , 1, 2, 4, and 8. To read syndrome bits from the CSR, CSR bit 2 must be set to 1 (diagnostic mode) and the CSR read. This operation allows syndrome bits for a single or double failure to be read, instead of the address bits normally read when CSR 2 is set to  $\emptyset$ .

2.3.7 Set Inhibit Mode (Bit 13) When this bit is set to  $\emptyset$ , diagnostic check mode and/or disable correction mode can operate over the entire memory.

When this bit is set to 1, the inhibit mode pointer inhibits either the first or second 16K from going into diagnostic check or disable correction mode.

This bit is a read/write bit reset by power up or BUS INIT.

#### 2.3.8 EUB Error Address Retrieval (Bit 14)

With bit 14 equal to  $\emptyset$ , a read to the CSR after an error fetches error address A17 through All. With bit 14 equal to 1, a read to the CSR fetches address A21 through A18.

Setting bit 14 to 1 has the side effect of preventing memory from entering the diagnostic check mode.

This bit is a read/write bit reset on power up and BUS INIT.

#### 2.3.9 Uncorrectable Error (Bit 15)

In normal operation or diagnotic check mode this bit is set on a DATI or DATIP when a double error is detected. Setting this bit also turns on a red LED on the board to indicate the error.

This bit is set in disable correction mode if a single or double error is detected.

This bit is a read/write bit reset on power up or BUS INIT.

#### 2.3.10 Notes on CSR Usage

Bit 1 (error correction disable) is usually set to 1 for diagnostic purposes, which allows data to be read or written into memory without interference from the error correction logic. If bit 1 is set to 1, you can clear a soft double error in memory by writing new data into one or both PDP-11 memory locations of the bad 22-bit word. Note that a soft double error may be caused by one hard error and one soft error, or two soft errors, within a 22-bit word (a hard double error cannot be cleared).

Bit 2 (diagnostic check mode) allows check bits in the MOS storage array to be read via the CSR. Right after a DATI bus cycle to memory (with bit 2 equal to 1), the CSR should be read with a DATI cycle to examine the check bits retrieved from the storage array. Note that a DATO cycle to the CSR destroys the retrieved check bits, but an error address recorded in the CSR is preserved.

The diagnostic check mode also provides a way to test the error correction logic by allowing the check bit pattern in a 22-bit word to be altered via the CSR. The desired check bit pattern should be written into CSR bits 11 -- 5 and bit 2 should be set to 1 with a DATO cycle to the CSR. A DATO cycle to memory should then be performed. Writing the appropriate check bit pattern in the storage array should cause detection and correction of a single-bit error during a subsequent memory read cycle. (Refer to Paragraph 4.3.11, Diagnostic Check Mode Usage.)

If bit 13 is set to 1, bits 1 and 2 in the CSR do not affect the portion of memory specified by bit 3. The system diagnostic can reside in the protected portion of memory. The diagnostic can then disable error correction and/or run the diagnostic check mode on the rest of the memory module, without being vulnerable to single-bit errors itself.

With bit 15 or 4 set to 1 and bits 14 and 2 cleared to  $\emptyset$ , you can retrieve the EUB error address (A21 -- All) as follows.

1. Read the CSR with a DATI bus cycle to obtain Al7 -- All.

2. Write a logical 1 into CSR bit 14 with a DATO bus cycle.

3. Read the CSR with a DATI bus cycle to obtain A21 -- A18.

When the memory is not in diagnostic mode (CSR bit 2 equals  $\emptyset$ ), data previously loaded into CSR bits 11 -- 5 cannot be read.

2-17

#### 2.3.11 More CSR Examples

The memory module does not inform the central processor unit (CPU) when a single error occurs. However, some operating systems poll the CSR periodically. If the operating system software sees that bit 4 is set, then it can perform a read to the CSR to read the address of the 1K block which contains the location of the 1-bit error. This address is bits All -- Al7 in CSR bits 5 -- 11.

6

| 15      | 14           | 13        | 12    | 11   | 10   | 9    | 8     | 7     | 6     | 5           | 4    | 3     | 2  | 1     | Ø      |     |

|---------|--------------|-----------|-------|------|------|------|-------|-------|-------|-------------|------|-------|----|-------|--------|-----|

| Ø       | ø            | Ø         | Ø     | A17  | A16  | A15  | A14   | A13   | A12   | A11         | 1    | Ø     | ø  | Ø     | 1      | -   |

|         | read<br>d on |           | hig   | her  | orde | r ad | dres  | ses,  | wri   | te b        | it ] | L4 to | a  | 1 (2  | Xs are | e   |

| 15      | 14           | 13        | 12    | 11   | 10   | 9    | 8     | 7     | 6     | 5           | 4    | 3     | 2  | 1     | Ø      |     |

| Ø       | 1            | Ø         | Ø     | X    | Х    | X    | X     | X     | X     | х<br>Х      | ø    | ø     | ø  | Ø     | 1      | -   |

|         |              | d th<br>5 |       | R ag | ain. | Thi  | s rea | ads a | addro | 9 <b>55</b> | bits | 5 A21 |    | - Al8 | 3 in ( | CSR |

| 15      | 14           | 13        | 12    | 11   | 10   | 9    | 8     | 7     | 6     | 5           | 4    | 3     | 2  | 1     | Ø      |     |

| ø       | 1            | Ø         | Ø     | Ø    | ø    | Ø    | A21 · |       | - 2   | A18         | ø    | ø     | ø  | Ø     | 1      | -   |

| То      | get          | the       | synd  | rome | bits | 5, S | et b  | it 2  | to a  | a l.        |      |       |    |       |        |     |

| 15      | 14           | 13        | 12    | 11   | 10   | 9    | 8     | 7     | 6     | 5           | 4    | 3     | 2  | 1     | ø      |     |

| Ø       | 1            | ø         | Ø     | x    | x    | X    | x     | x     | х     | X           | ø    | Ø     | 1  | Ø     | 1      | -   |

| Now<br> |              | d the     | e CSI | R. E | rror | synd | drome | e bit | :s S8 | 3           | SX   | are   | in | CSR   | bits   | 5   |

| 15      | 14           | 13        | 12    | 11   | 10   | 9    | 8     | 7     | 6     | 5           | 4    | 3     | 2  | 1     | Ø      |     |

| Ø       | 1            | Ø         | Ø     | Ø    | S 8  | S 4  | s 2   | s1    | SØ    | SX          | Ø    | Ø     | 1  | Ø     | 1      | -   |

| Now     | wri          | te C      | SR b  | it 2 | to   | Ø to | res   | ume   | norma | al o        | pera | ation | •  |       |        |     |

2-18

To load check bits into the CSR, write the desired check bits into CSR bits 10 -- 5 and enable diagnostic mode.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | Ø     |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-------|

|    |    |    | ø  |    |    |   |   |   |   |   |   |   |   |   | <br>Ø |

Now, a write to a memory address takes these check bits from the CSR instead of from the EDC (error detection and correction circuit).

A read to a memory address takes the check bits stored in memory and loads them into bits 5 --10 in the CSR.

2.3.12 Summary Data Condition Tables The following tables are summaries of the memory actions for each possible condition of data in each operating mode of memory.

Protected refers to the memory area when the module is in a diagnostic mode, but the data transaction is in the first or second 16K of memory, and unconditional protection of that area is enabled. Unprotected refers to any other area of memory.

| Normal operating mode                                     | Data read from memory and placed on<br>bus                                                                                      |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Diagnostic mode<br>/protected                             | Data read from memory and placed on<br>bus like normal read cycle                                                               |

| Diagnostic mode<br>/unprotected                           | Data read from memory and placed on<br>bus like normal read cycle check<br>bits read from memory are logged in<br>CSR bits 5 10 |

| Disable correction mode<br>/protected                     | Data read from memory and placed on<br>bus like normal read cycle                                                               |

| Disable correction mode<br>/unprotected                   | Data read from memory and placed on<br>bus like normal read cycle                                                               |

| Diagnostic and disable<br>correction mode<br>/protected   | Data read from memory and placed on<br>bus like normal read cycle                                                               |

| Diagnostic and disable<br>correction mode<br>/unprotected | Data read from memory and placed on<br>bus like normal read cycle check<br>bits read from memory are logged in<br>CSR bits 5 10 |

Table 2-4 Read, No Errors

| Normal operating mode                                     | CSR 4 H is set. Data is corrected by<br>EDC before it is placed on bus. If CSR<br>15 H is not set, All A21 and error<br>syndrome bits are latched in CSR. If<br>CSR 15 H was set on a previous DBE,<br>but not cleared by software, there is<br>no logging of the SBE so information<br>from previous error can be read. |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Diagnostic mode<br>/protected                             | CSR 4 H is set. Data is corrected by<br>EDC before it is placed on bus.<br>Addresses and error syndromes are not<br>logged in CSR.                                                                                                                                                                                       |

| Diagnostic mode<br>/unprotected                           | CSR 4 H is set. Data is read from<br>memory and corrected by EDC before it<br>is placed on bus. Check bits read from<br>memory are logged in CSR bits 5 10.<br>No addresses or error syndrome bits<br>are logged.                                                                                                        |

| Disable correction mode<br>/protected                     | CSR 4 H is not set. Data is corrected<br>by EDC before it is placed on the bus.<br>Addresses and error syndromes are not<br>logged in CSR.                                                                                                                                                                               |

| Disable correction mode<br>/unprotected                   | CSR 15 H and CSR 4 H are set. With<br>error correction disabled, a single<br>bit error becomes an uncorrectable<br>error. All A21 and error syndromes<br>are logged in CSR. If CSR Ø H is set,<br>BUS PB L is asserted on bus at same<br>time as uncorrected data.                                                       |

| Diagnostic and disable<br>correction mode<br>/protected   | CSR 4 H is set. Data is corrected by<br>EDC before it is placed on bus.<br>Addresses and error syndromes are not<br>logged in CSR.                                                                                                                                                                                       |

| Diagnostic and disable<br>correction mode<br>/unprotected | CSR bits 4 and 15 are set. Data is<br>read from memory and placed on bus.<br>No correction takes place. Check bits<br>read from memory are logged in CSR<br>bits 5 10. Addresses and syndromes<br>are not logged.                                                                                                        |

6

2

۲

٩.

10

| Normal operating mode                                     | CSR 15 H is set. All A2l and error<br>syndromes are latched in CSR. Red LED<br>turns on. If CSR Ø H is set, BUS PB L<br>is asserted on bus at same time as<br>uncorrected data.                                                                   |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Diagnostic mode<br>/protected                             | CSR 15 H is set. Red LED turns on. If<br>CSR $\emptyset$ H is set, BUS PB L is asserted<br>on bus at same time as uncorrected<br>data. No other information is logged<br>in CSR.                                                                  |

| Diagnostic mode<br>/unprotected                           | CSR 15 H is set. Red LED turns on. If<br>CSR Ø H is set, BUS PB L is asserted<br>on bus at same time as uncorrected<br>data. Check bits read from memory are<br>logged in CSR bits 5 10. No<br>addresses or error syndromes are<br>logged in CSR. |